## EFFICIENT CALCULATION OF THE IMPACT OF DECOUPLING CAPACITORS FOR POWER DISTRIBUTION NETWORK DESIGN AT PCB AND PACKAGE LEVEL

Francesco de Paulis, Antonio Orlandi

Dipartimento di Ingegneria Industriale e dell'Informazione e di Economia, Università degli Studi dell'Aquila

Via G. Gronchi 18, Loc. Pile, 67100 L'Aquila

With power distribution networks (PDNs) requiring ever tighter limits on voltage ripple [1], demand is increasing for tools to optimize PDN impedance by automatically selecting a minimal number of capacitors to decrease PDN impedance below the target impedance [2]. This work aims to propose a fast method for efficiently calculating the PDN impedance such that optimization methods requiring a typically prohibitive number of impedance calculations become viable.

The impedance matrix of a PDN can be modified to add a list of capacitors to corresponding ports by dividing the matrix into four sections as in (1) such that p is a list of all ports to be left empty and L is a list of all ports to be loaded with a capacitor.  $Z_{dd}$  is a diagonal matrix of the impedances of all capacitors to be added, with each row and column corresponding to the port at the same index in L [3].

$$\overline{\overline{Z_{new}}} = \overline{\overline{Z_{pp}}} - \overline{\overline{Z_{pL}}} \left( \overline{\overline{Z_{dd}}} + \overline{\overline{Z_{LL}}} \right)^{-1} \overline{\overline{Z_{Lp}}}$$

(1)

The time taken to compute (1) scales quadratically to the length of p. The time also monotonically increases with the length of L, however the exact relation is nonlinear and dependent upon the method used to take the matrix inverse. Because of the computational resources required, it is typically best to minimize the number of times (1) is executed, necessitating a method to infer the optimal capacitor(s) to be added without directly calculating their impact on the complete multiport system impedance such as [4, 5].

It is possible to reduce the matrices used in (1) such that only a single entry in the impedance matrix is calculated, resulting in (2). This calculation time does not scale with the output matrix size, significantly reducing calculation time.

$$Z_{new_{ij}} = Z_{ij} - \overline{Z_{\iota L}} \left( \overline{Z_{dd}} + \overline{Z_{LL}} \right)^{-1} \overline{Z_{LJ}}$$

(2)

Because this calculation only yields a single member of the impedance matrix, it cannot be solely used to create an iterative optimization algorithm, which would require a full new impedance matrix with each step. However, because of the low computational requirement, it does allow for efficient testing of how adding one or more capacitors would affect a single matrix member, for example, the self-impedance at the package port. This makes viable a class of optimization algorithms which select capacitors using a full sweep of available options, selecting based on which gives the most desired effect on the PDN impedance.

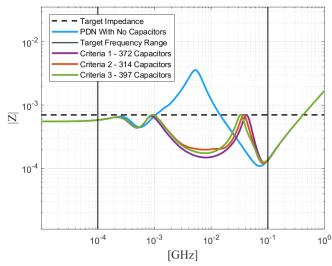

This work proposes three sets of criteria for evaluating the optimal capacitor based on the effect on the self-impedance at the package port. The first is based on the poles and zeroes method presented in [4], selecting the capacitor which best pushes PDN impedance below the target from low to high frequency. The second selects the capacitor which best reduces the total area under the impedance curve as used for feedback for the algorithm in [5]. The third selects the capacitor which best reduces the average height of all local maxima in the impedance spectrum. Each algorithm will test a full sweep of all possible capacitors placed on all available ports on the PDN using (2), one capacitor at a time. The results of all tested

capacitors will be compared, the best will be selected, and the full PDN impedance will be updated using (1) to prepare for the next iteration, until a target impedance is met. The test PDN used has 1,043 capacitor ports with 10 available capacitor varieties for a total of 10,430 executions of (2) for the first capacitor selection, reducing by 10 with each added capacitor.

Fig. 1. Full Sweep Decoupling Capacitor Optimization Results

Table I shows the time taken to complete the first capacitor selection for each algorithm, which in each case required the same number of impedance calculations. In the last column, it also shows the total time taken, for which the number of calculations varies by how many capacitors were necessary to meet the target, as shown in Fig. 1. This data confirms that simplifying matrix impedance calculations can lead to impedance computation being efficient enough to make even full sweep based optimization viable as a method to select decoupling capacitors.

| Criteria | First Capacitor Selection Time (s) |                       | Total            |

|----------|------------------------------------|-----------------------|------------------|

|          | (2), 10 <sup>4</sup> Executions    | (1), Single Execution | Runtime<br>(min) |

| 1        | 0.8273                             | 11.53                 | 47.92            |

| 2        | 0.6951                             | 10.01                 | 40.00            |

| 3        | 0.7269                             | 10.93                 | 46.14            |

TABLE I. TOTAL CALCULATION TIME

- [1] B. Zhao et al., "System Level Power Integrity Analysis with Physics-Based Modeling Methodology", 2018 IEEE Symposium on Electromagnetic Compatibility Signal Integrity and Power Integrity (EMC SI PI), pp. 379-384.

- [2] S. Liang *et al.*, "Decoupling Capacitor Optimization to Achieve Target Impedance in PCB PDN Design," 2021 IEEE International Joint EMC/SI/PI and EMC Europe Symposium, Raleigh, NC, USA, 2021, pp. 967-972.

- [3] Muhammet Hilmi Nisanci and F. de Paulis, "Efficient Analytical Prediction of the Cavity Resonant Behavior of PEC-PMC Metallic Enclosures and Packages," *IEEE Transactions on Electromagnetic Compatibility*, vol. 63, no. 1, pp. 93–102, Aug. 2020.

- [4] Y. Ding et al., "System Level PDN Impedance Optimization Utilizing the Zeros of the Decoupling Capacitors," 2023 IEEE Symposium on Electromagnetic Compatibility & Signal/Power Integrity (EMC+SIPI), Grand Rapids, MI, USA, 2023, pp. 249-254.

- [5] F. de Paulis *et al.*, "Efficient Iterative Process Based on an Improved Genetic Algorithm for Decoupling Capacitor Placement at Board Level," *Electronics*, vol. 8, no. 11, pp. 1219–1219, Oct. 2019.